Cadence Xtensa Xplorer is the central integrated development environment for the Cadence Xtensa® processor family—highly configurable and extensible RISC processor IP cores. Unlike traditional IDEs for fixed-instruction-set architectures (like ARM), Xtensa Xplorer is used to define, configure, implement, and program custom processors. It provides a complete workflow: from architectural exploration (adding custom instructions, registers, and execution units) through automatic generation of the hardware RTL, software toolchain (compiler, debugger), and simulation models, to final software development and optimization. It is the toolchain for creating a “processor that fits the problem”.

Xtensa Xplorer is a specialized IDE for high-performance, configurable computing:

SoC Architects & Designers defining custom processor cores for AI/ML, audio, vision, and communications applications.

Embedded Software Engineers writing and optimizing code for Xtensa processors.

DSP Algorithm Developers implementing and tuning signal processing workloads (5G, Radar, Audio Codecs).

FPGA/ASIC Prototyping Engineers using Xtensa cores in programmable logic or custom silicon.

Performance Analysis Engineers profiling and tuning system-level performance, power, and memory usage.

Research & Development Teams in semiconductor companies, OEMs, and tech firms building domain-specific accelerators.

Tensilica Instruction Extension (TIE) Language: Core technology for describing custom instructions, registers, and execution units. Xplorer provides editors, compilers, and simulators for TIE.

Interactive Configuration GUI: Visually select and configure base Xtensa core features (cache sizes, interrupts, interfaces, MMU) and add predefined extension packs (DSP, AI, Controller).

Automated Hardware/Software Co-Generation: With a configuration defined, Xplorer automatically generates:

Synthesizable RTL for the custom processor.

Optimized C/C++ Compiler (XCC) tailored to the new instructions.

Cycle-Accurate Instruction Set Simulator (ISS).

Complete Software Development Kit (SDK) including debugger (XD), profiler, and RTOS awareness.

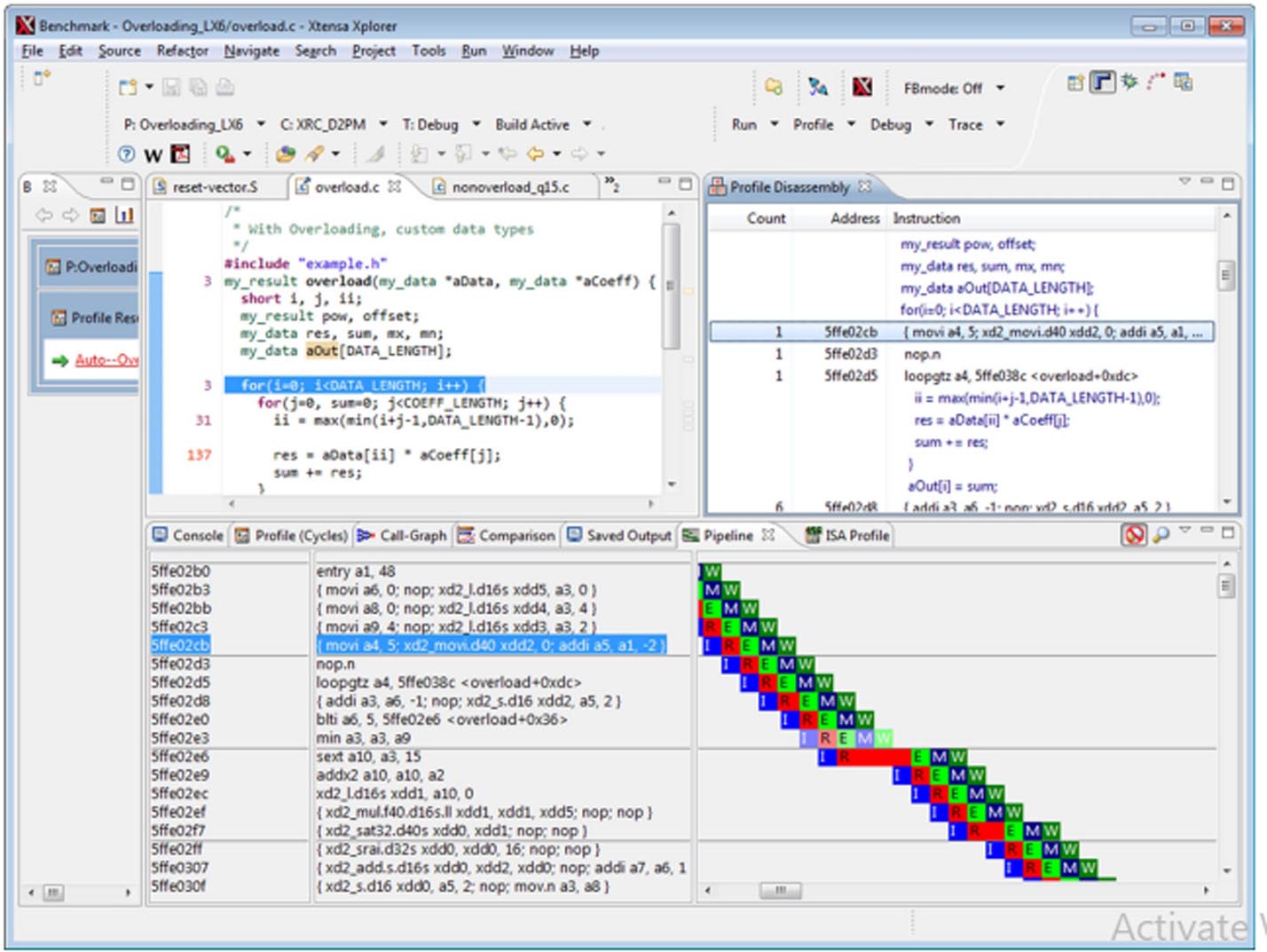

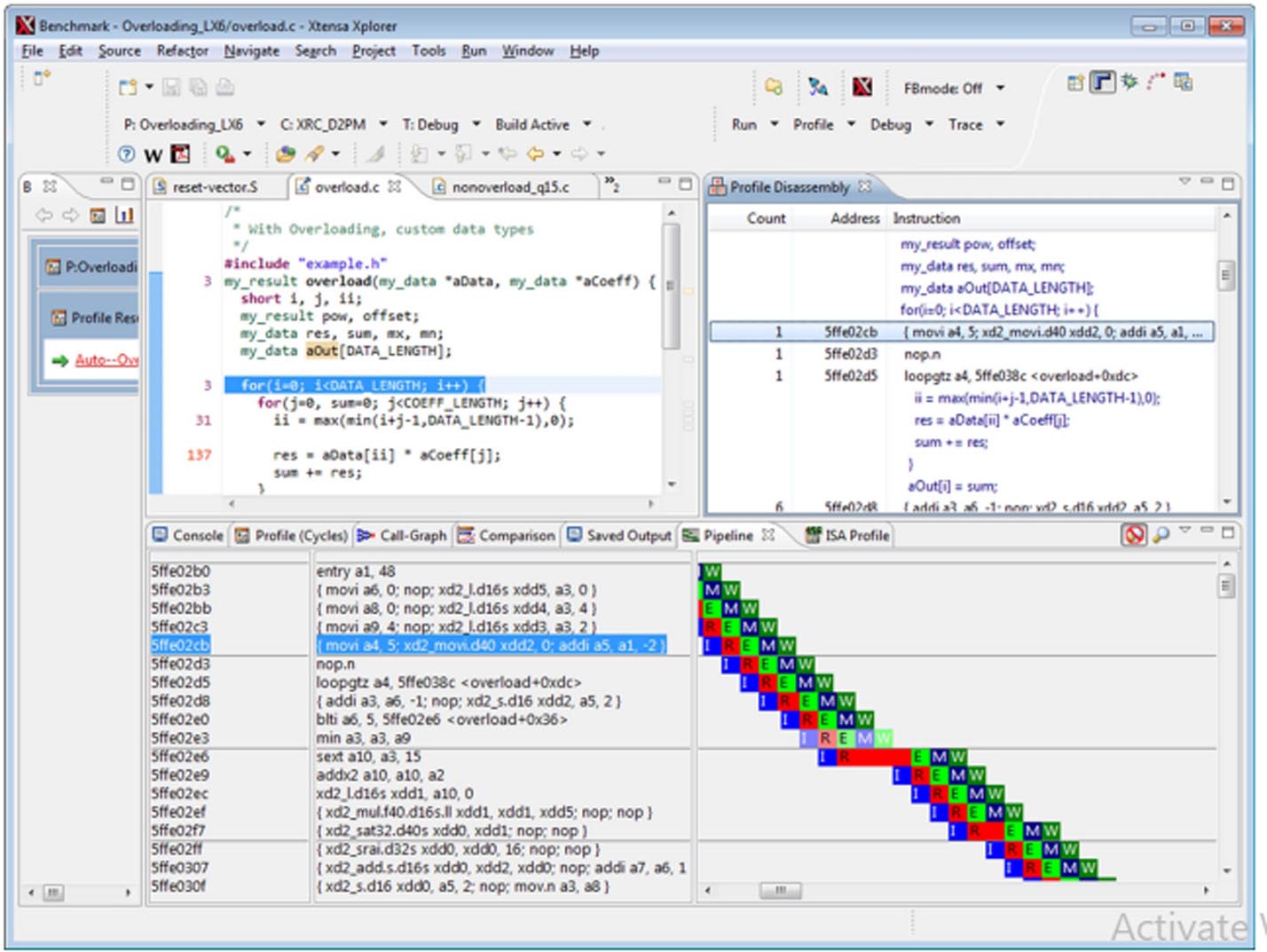

Eclipse-Based IDE: Familiar environment with project management, code editor, and build system integration.

Advanced Debugger (Xplorer Debugger): Multi-core debug, non-intrusive tracing, hardware/software co-debug, and real-time execution on FPGA prototypes or silicon.

Profiling & Performance Analysis: Xtensa Profiler and Performance Monitor tools to identify bottlenecks in C code and assembly, visualize pipeline stalls, and measure cache efficiency.

SystemC/TLM-2.0 Modeling: Create fast, transaction-level models of the configured processor for early system-level simulation and virtual prototyping.

Seamless Cadence Flow Integration: Direct links to JasperGold for formal verification, Palladium/Z1 for hardware emulation, and Spectre X for analog/mixed-signal simulation.

Multi-Core & Heterogeneous System Modeling: Configure and program systems with multiple Xtensa cores (HiFi Audio, Vision P6, etc.) and custom hardware accelerators.

Power Analysis Integration: Feed activity data into Cadence Joules for RTL-to-gate-level power estimation of the custom processor.

OS: Red Hat Enterprise Linux (RHEL) 7.6-8.6 / CentOS 7.6-8.6, or Ubuntu 18.04 LTS – 22.04 LTS

CPU: 64-bit x86, 8+ cores (16+ recommended for simulation speed)

RAM: 32 GB minimum (64 GB+ recommended for large simulations and multi-core systems)

Storage: 100 GB+ free disk space (SSD/NVMe critical for build performance)

GPU: Not required for core functionality, but beneficial for GUI (NVIDIA/AMD with modern drivers)

OS: Windows 10/11 Pro 64-bit

Note: Often run in a Linux virtual machine (VMware, VirtualBox) or via Windows Subsystem for Linux (WSL2) for full compatibility with the backend toolchain.

Price: 325 $

Price Currency: $

Operating System: Windows

Application Category: Embedded Systems

Reviews

There are no reviews yet.