Sigasi Visual HDL Enterprise Edition is a powerful IDE tailored for Hardware Description Language (HDL) and Hardware Verification Language (HVL) development. Built on the Eclipse platform, it provides intelligent code editing, real-time error checking, advanced navigation, and project management features specifically for the complexities of hardware design. It integrates with major EDA toolchains (simulators, synthesis, version control) to boost productivity, improve code quality, and reduce debugging time in FPGA and ASIC development projects.

Sigasi Visual HDL Enterprise Edition is a specialized integrated development environment (IDE) designed for Digital Design Engineers, FPGA/ASIC Designers, Verification Engineers, RTL Coders, and Hardware Development Teams who write, analyze, and manage VHDL, Verilog, SystemVerilog, and e code for electronic hardware design.

Intelligent Code Editor: Advanced syntax highlighting, autocompletion, template insertion, and real-time semantic error checking (linting) for VHDL, Verilog, and SystemVerilog.

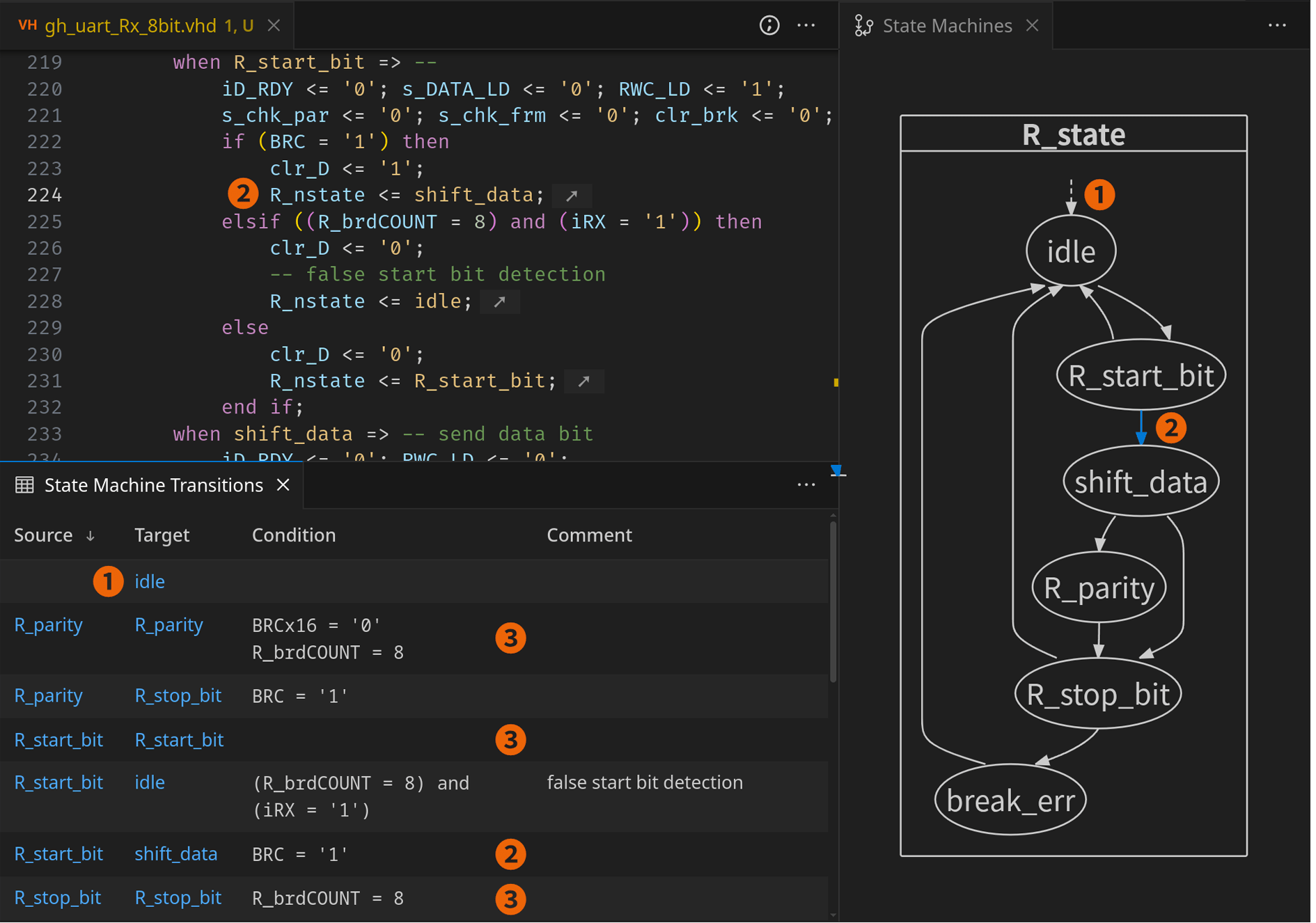

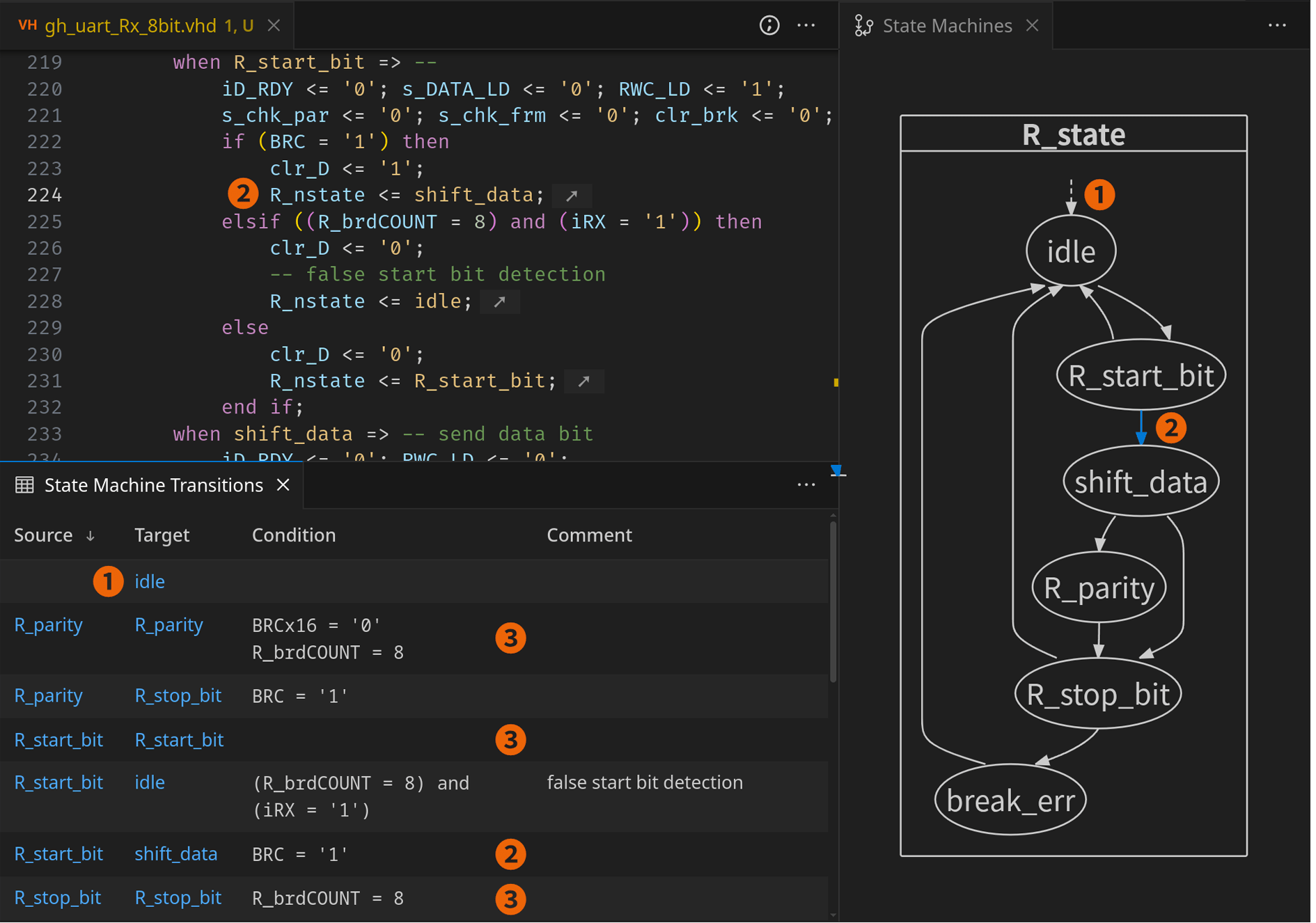

Hyper-Speed Navigation & Understanding: Instant navigation to declarations, definitions, and instantiations. Visualizations of design hierarchy, block diagrams, and state machine diagrams extracted directly from the code.

Advanced Refactoring & Code Quality Tools: Automated refactoring (renaming, moving files, extracting modules) and built-in style checkers to enforce coding standards (e.g., HDLint).

Integrated Documentation: Generates documentation (HTML, PDF) from code comments and automatically creates architecture diagrams.

Seamless EDA Tool Integration: Works with industry simulators (ModelSim, Xcelium, VCS), synthesis tools (Vivado, Quartus), and build systems (Make, CMake) via command-line integration or plugins.

Team Collaboration & Version Control: Excellent support for Git, SVN, and Perforce, with features for code reviews, diff viewing, and project sharing.

This release focuses on enhanced language support, performance, and developer experience for large-scale enterprise projects.

Expanded SystemVerilog & UVM Support: Deeper analysis and support for the latest SystemVerilog constructs and Universal Verification Methodology (UVM) libraries used in advanced verification.

Performance & Scalability Improvements: Optimized indexing and background analysis engines for faster operation on massive codebases with millions of lines of code.

Enhanced Debug Integration: Tighter integration with simulator waveforms; ability to trace simulator errors back to specific lines in the source code.

New Code Intelligence Features: More powerful autocomplete suggestions, improved “find all references” across very large projects, and better handling of macro-heavy code.

Updated UI & Developer Experience: Refined user interface, new keyboard shortcuts, and customizable workspace layouts to streamline common hardware design workflows.

OS: Windows 10/11 (64-bit), Linux (Red Hat, CentOS, Ubuntu LTS), or macOS.

CPU: Multi-core processor.

RAM: 8 GB minimum (16 GB+ recommended for large designs).

Storage: 2 GB free space + space for projects.

Java: Requires a 64-bit Java Runtime Environment (JRE 11 or 17).

Price: 325 $

Price Currency: $

Operating System: Windows

Application Category: Electronics

Reviews

There are no reviews yet.