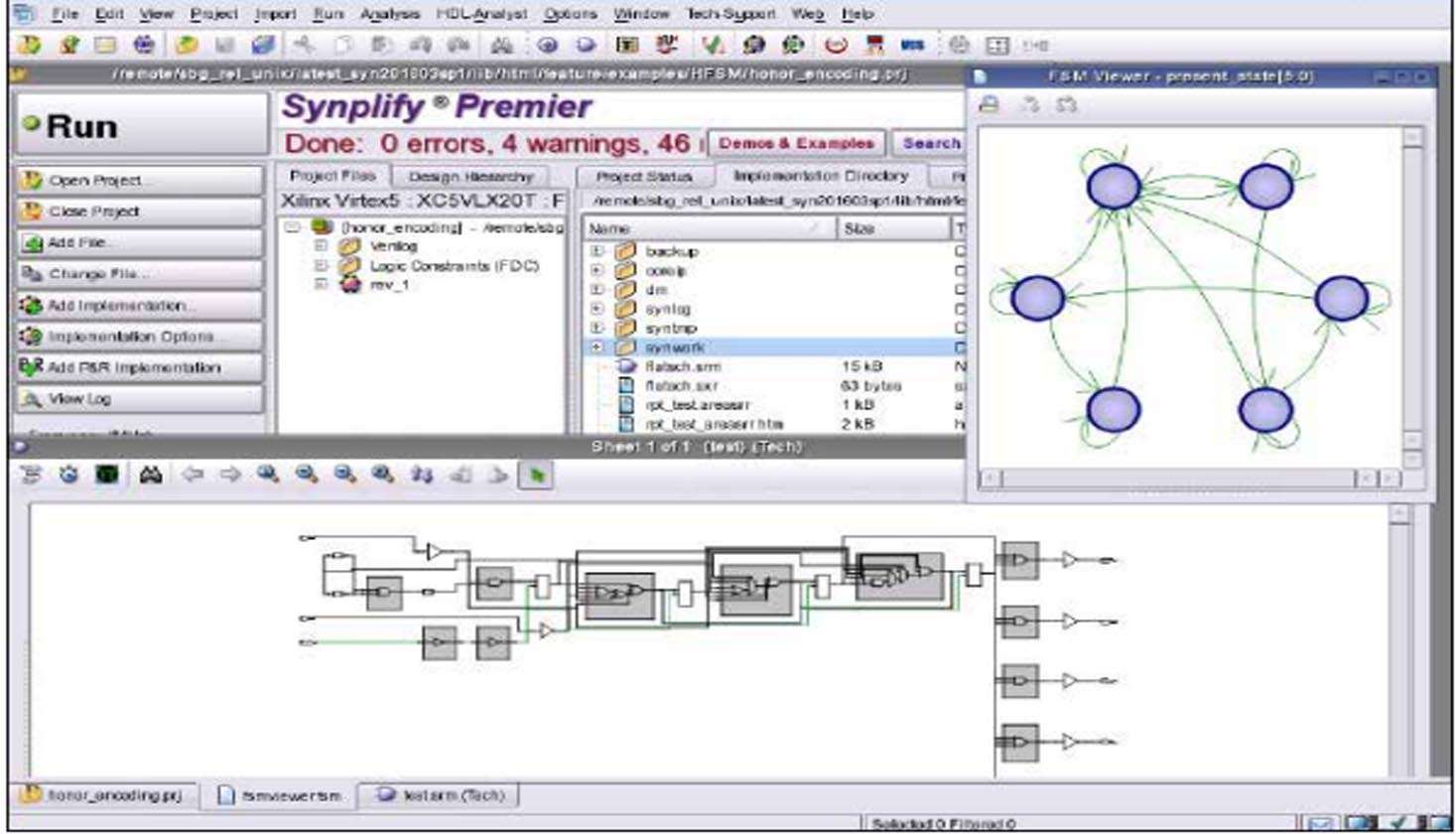

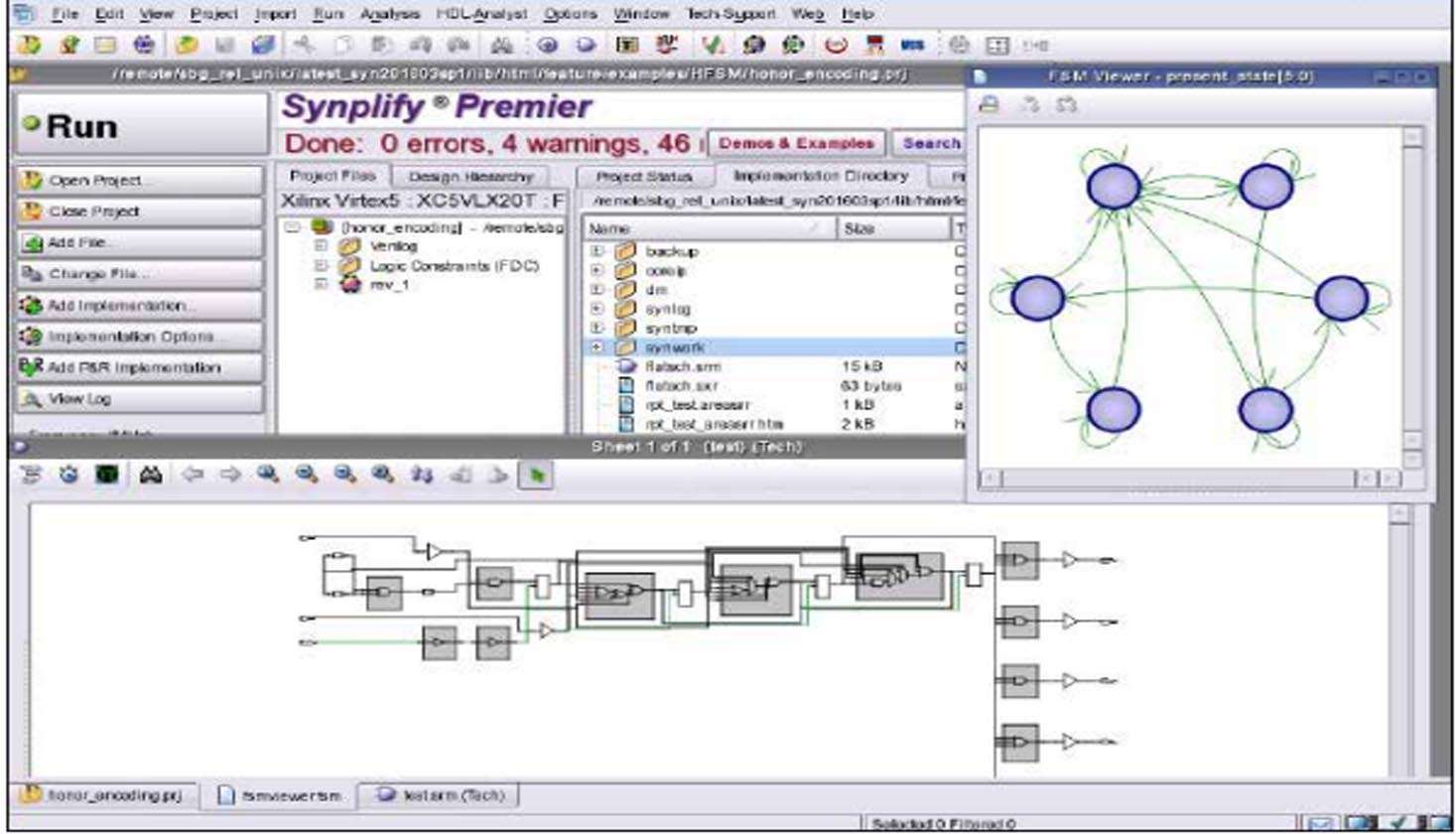

Synopsys Synplify FPGA is a premier FPGA synthesis and implementation tool that delivers superior quality of results (QoR) and faster compile times compared to vendor tools. It combines advanced optimization algorithms with intuitive design analysis to help designers achieve higher performance and lower power consumption. The tool supports a comprehensive design flow from RTL or high-level C/C++ code to optimized FPGA netlists, with particular strengths in timing closure, area optimization, and debug capabilities.

Synplify FPGA is optimized for FPGA design professionals:

FPGA Design Engineers targeting Xilinx, Intel, Microchip, and Lattice devices

Digital Design Engineers converting C/C++/SystemC to RTL via high-level synthesis

ASIC Prototyping Teams using FPGAs for pre-silicon validation

Embedded Systems Developers implementing DSP and vision algorithms on FPGAs

Research & Academic Users in digital design and reconfigurable computing

Verification Engineers using FPGA-based prototyping for system validation

Ultra-High Performance Synthesis: Multi-core optimized algorithms for 2-3x faster synthesis vs. vendor tools

Timing-Driven Optimization: Advanced physical synthesis with accurate timing models for all major FPGA families

Power Optimization: Clock gating, operand isolation, and activity-driven power reduction

Incremental Compilation: Re-synthesize only modified modules, reducing iteration time by up to 70%

High-Level Synthesis (HLS): Convert C, C++, SystemC to optimized RTL with pragma-based optimization

Graphical Debug Environment: Cross-probing between RTL, schematic, and timing reports

Design Vision Analyzer: Interactive timing analysis and critical path optimization

Constraint Management: Advanced SDC constraint editing and validation

Xilinx: Full support for Versal, UltraScale+, 7-series, and Spartan families

Intel: Agilex, Stratix, Arria, Cyclone, and Max families

Microchip: PolarFire, SmartFusion, IGLOO, and ProASIC

Lattice: Certus-NX, CrossLink-NX, ECP5, and MachXO families

Formal Verification: Equivalence checking between RTL and synthesized netlist

ASIC Prototyping Flow: Multi-FPGA partitioning and automatic inter-FPGA routing

Debug Integration: Native support for Vivado/Xilinx debug cores and SignalTap

AI-Driven Synthesis (Synplify AI Engine): New machine learning algorithms that predict optimal synthesis strategies based on design characteristics, improving QoR by 15-25%

3D-IC FPGA Support: Enhanced synthesis for Xilinx and Intel 3D FPGA devices with intelligent die-to-die optimization

Quantum-Safe Cryptography IP: New optimized IP libraries for post-quantum cryptography algorithms

Enhanced HLS with LLVM 17: Updated compiler infrastructure with improved vectorization and loop optimization

Unified Constraint Manager: Visual constraint editing with real-time timing impact analysis

Cloud-Native Flow: Direct integration with AWS, Azure, and Google Cloud for elastic compute scaling

Enhanced Versal AI Engine Support: Improved synthesis for Versal AI Engine and NoC integration

Real-Time Power Analysis: Dynamic power estimation during synthesis iterations

AI-Powered Timing Closure: Predictive timing optimization that anticipates routing congestion

Enhanced Formal Verification: Faster equivalence checking with improved counterexample generation

Multi-FPGA Debug Integration: Unified debug across partitioned FPGA systems

Minimum Requirements:

OS: Windows 10/11 Pro 64-bit (22H2 or later)

CPU: Intel Core i7-12700 or AMD Ryzen 7 5800X (8+ cores)

RAM: 32 GB (64 GB recommended for large designs)

GPU: NVIDIA GTX 1660 or equivalent (4 GB VRAM)

Storage: 100 GB free SSD space

FPGA Vendor Tools: Vivado 2024.1+, Quartus Prime 23.4+

Recommended Configuration:

OS: Windows 11 Pro for Workstations

CPU: Intel Core i9-14900K or AMD Ryzen 9 7950X (24+ threads)

RAM: 128 GB DDR5

GPU: NVIDIA RTX 4080 (16 GB VRAM) for AI/ML features

Storage: 1 TB NVMe Gen4 SSD + 2 TB secondary SSD

Network: 2.5 GbE for license/server access

Price: 325 $

Price Currency: $

Operating System: Windows

Application Category: Electronics

Reviews

There are no reviews yet.