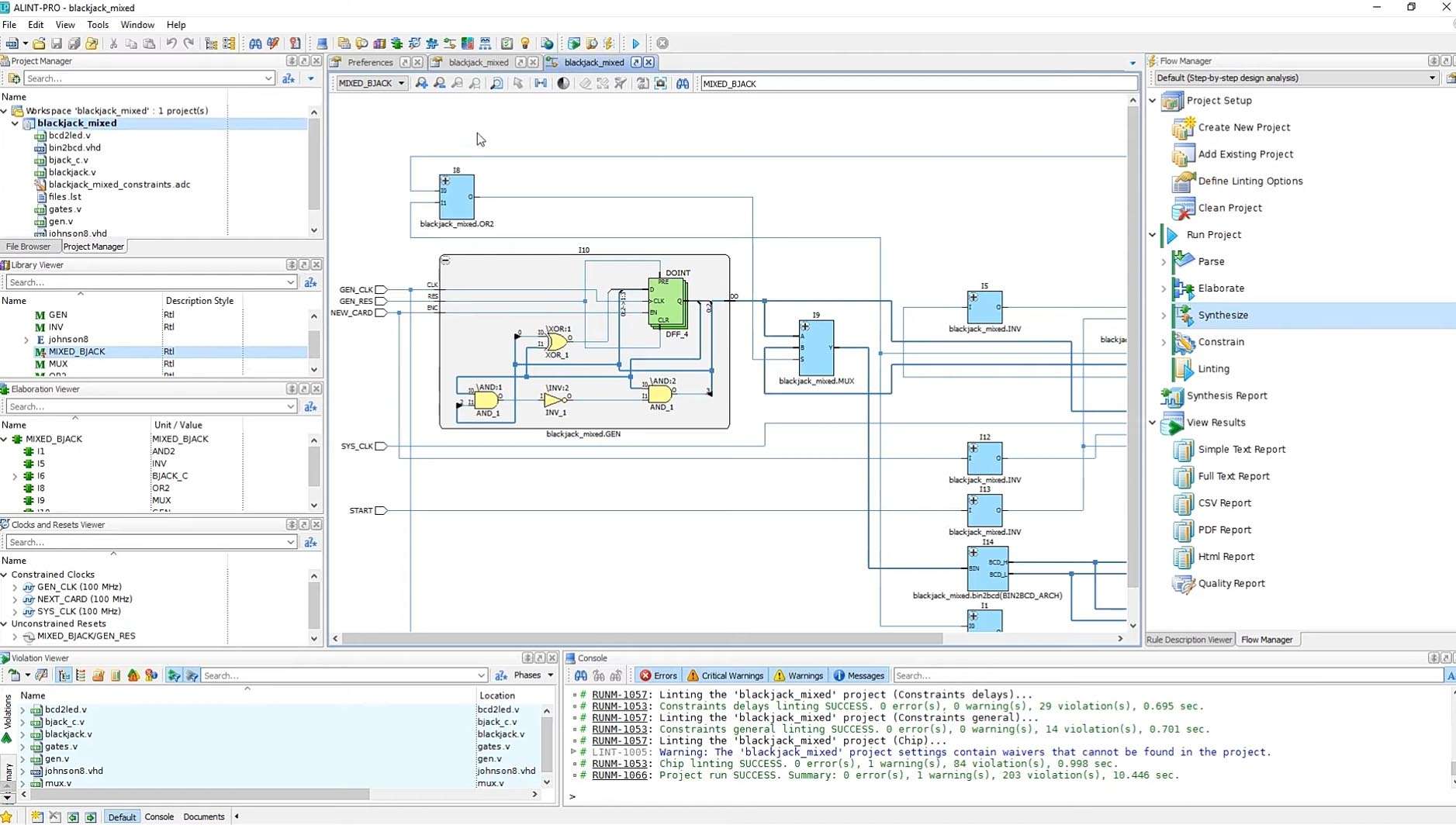

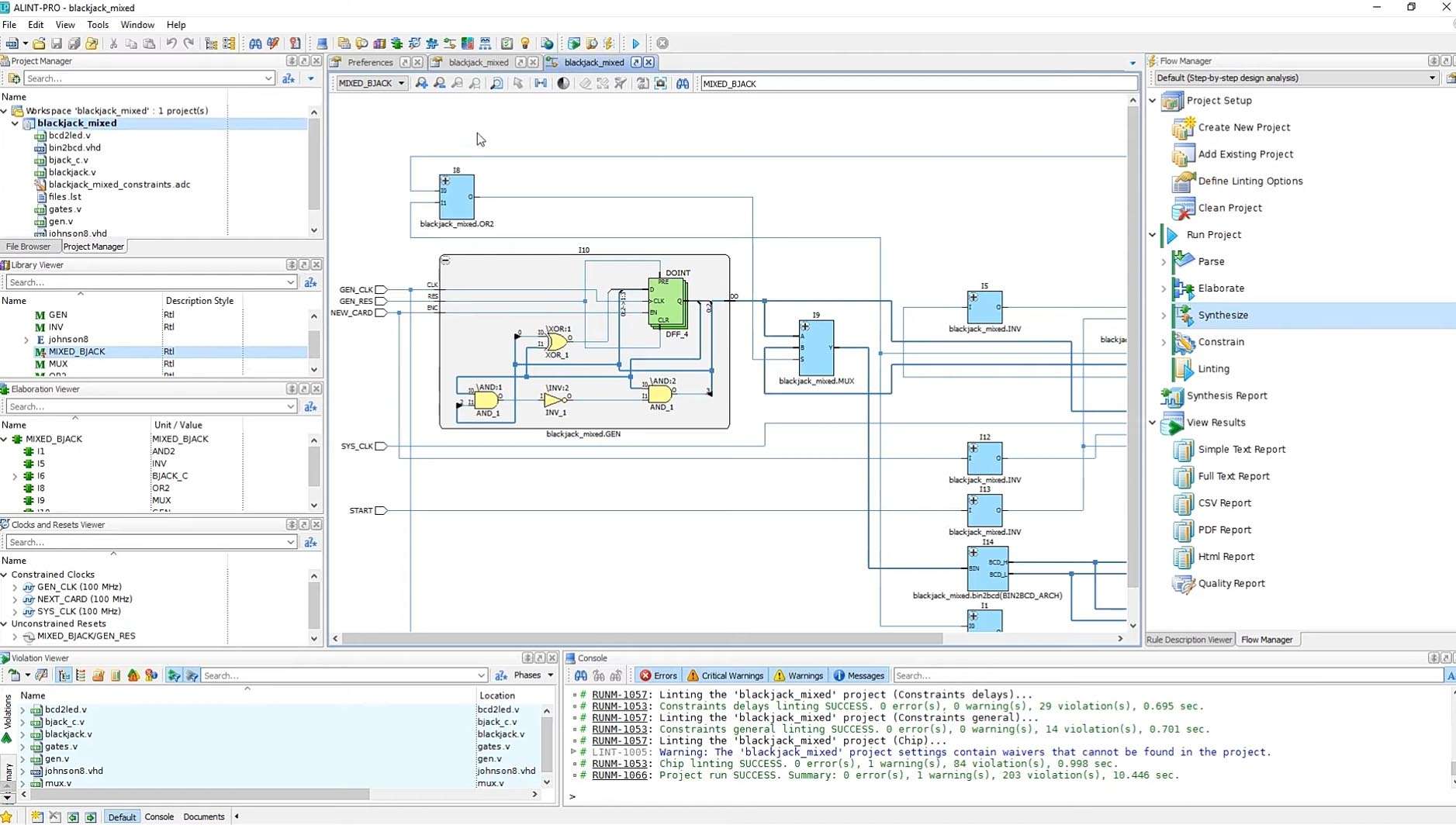

Aldec ALINT-PRO is a comprehensive static design verification and linting tool for digital hardware designs. It analyzes RTL source code without simulation to identify design flaws, coding style violations, synthesis issues, and potential reliability problems early in the development cycle. By enforcing project-specific or industry-standard coding rules (like DO-254, MISRA-C, or custom guidelines), it improves design quality, reduces simulation debug time, and ensures code consistency across teams and projects for ASIC and FPGA implementations.

Aldec ALINT-PRO is a specialized design verification software designed for ASIC/FPGA Design Engineers, Verification Engineers, Design Methodology Engineers, and Project Leads who need to perform advanced design rule checking, coding standard enforcement, and RTL (Register Transfer Level) linting for VHDL, Verilog, SystemVerilog, and mixed-language projects.

Advanced RTL Linting & Rule Checking: Extensive library of built-in and customizable rules for checking coding style, synthesizability, clock domain crossing (CDC), reset domain crossing (RDC), and industry best practices.

Support for Multiple HDLs: Deep analysis of VHDL, Verilog, SystemVerilog (for design), and mixed-language projects.

CDC/RDC Analysis: Sophisticated static analysis to identify and report on potential metastability issues arising from clock and reset domain crossings, a critical step for reliable silicon.

Compliance & Standards Checking: Pre-configured rule sets for safety-critical standards (DO-254, ISO 26262) and coding guidelines (MISRA-C for HDL, company-specific style guides).

Interactive Debug & Waiver Management: Integrated debugging environment to trace rule violations to source code and a comprehensive waiver management system for filtering false positives or approved deviations.

Integration with Design Flows: Seamlessly integrates into industry-standard design flows, with interfaces to Aldec’s Active-HDL/Riviera-PRO simulators, version control systems, and CI/CD pipelines.

This release focuses on enhanced analysis engines, expanded language support, and improved usability for large-scale projects.

Enhanced SystemVerilog & UVM Support: Deeper analysis of complex SystemVerilog constructs and improved checking for Universal Verification Methodology (UVM) code used in testbenches.

Next-Generation CDC/RDC Analysis Engine: Improved algorithms for more accurate detection and reporting of complex multi-clock and multi-reset domain crossing scenarios with reduced false positives.

Expanded Safety & Security Rule Packs: New and updated rule sets for functional safety (ISO 26262, IEC 61508) and hardware security vulnerabilities.

Improved Performance & Scalability: Optimized for faster analysis of massive, multi-million line codebases common in modern SoC designs.

Modernized GUI & Reporting Dashboard: Redesigned user interface with enhanced visualization of results, trend analysis, and project health dashboards.

OS: 64-bit Linux (RHEL, CentOS, Ubuntu) or Windows 10/11.

CPU: Multi-core Intel or AMD processor.

RAM: 16 GB minimum (32 GB+ recommended for large designs).

Storage: 10 GB+ free disk space.

Other: License manager (FlexNet) for network installations.

Price: 325 $

Price Currency: $

Operating System: Windows

Application Category: Electronics

Reviews

There are no reviews yet.