Gowin EDA, often referred to as Gowin FPGA Designer or GowinSuite, is the official, complete integrated development environment (IDE) provided free of charge by Gowin Semiconductor for their FPGA and FPGA-based SoC products. It is a full-featured EDA toolchain that includes everything needed to take a design from concept to a programmed bitstream: synthesis, place-and-route, timing analysis, and in-system debugging. As the proprietary tool for a specific FPGA vendor, it is optimized for Gowin’s chip architectures, offering a cost-effective and powerful solution for leveraging their low-power, low-cost FPGA families.

It provides a critical accessible entry point into the FPGA market, enabling both professionals and learners to develop for Gowin FPGAs without the high licensing fees associated with some other vendor tools.

Key Features & Capabilities

Gowin EDA is a complete, vendor-specific toolchain comparable to Intel Quartus (for Intel FPGAs) or Xilinx Vivado (for AMD FPGAs).

Complete FPGA Development Flow:

1. Design Entry:

· Integrated Text Editor: For writing HDL code (Verilog, VHDL, SystemVerilog support).

· Schematic Capture: Graphical entry for block-based design (less common in modern workflows).

· IP Core Generator (GWIN): Generate and integrate pre-verified intellectual property blocks like PLLs, memory controllers, SerDes, and soft-core CPUs (e.g., Gowin’s ARM Cortex-M3 hard processor in their SoCs).

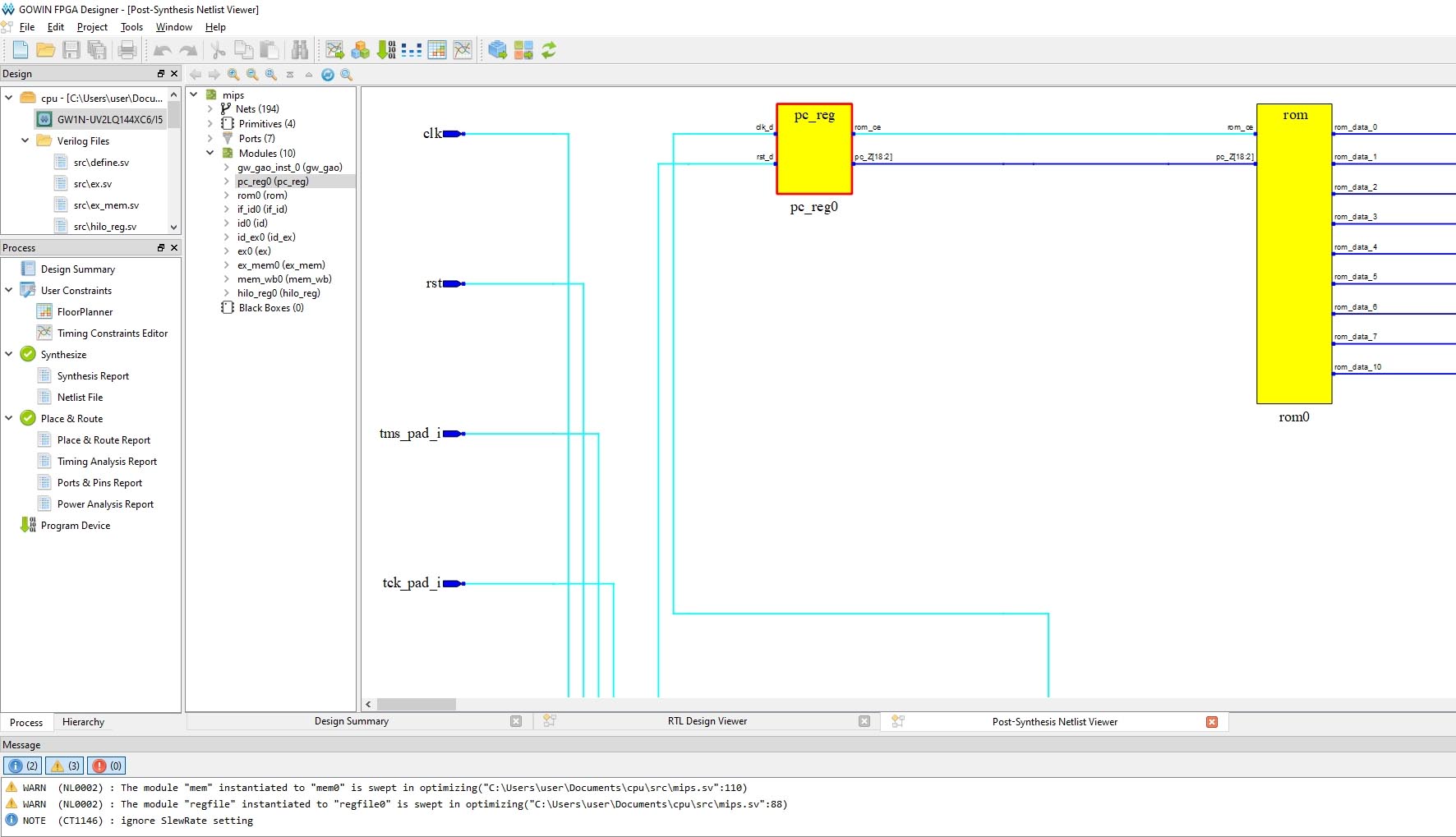

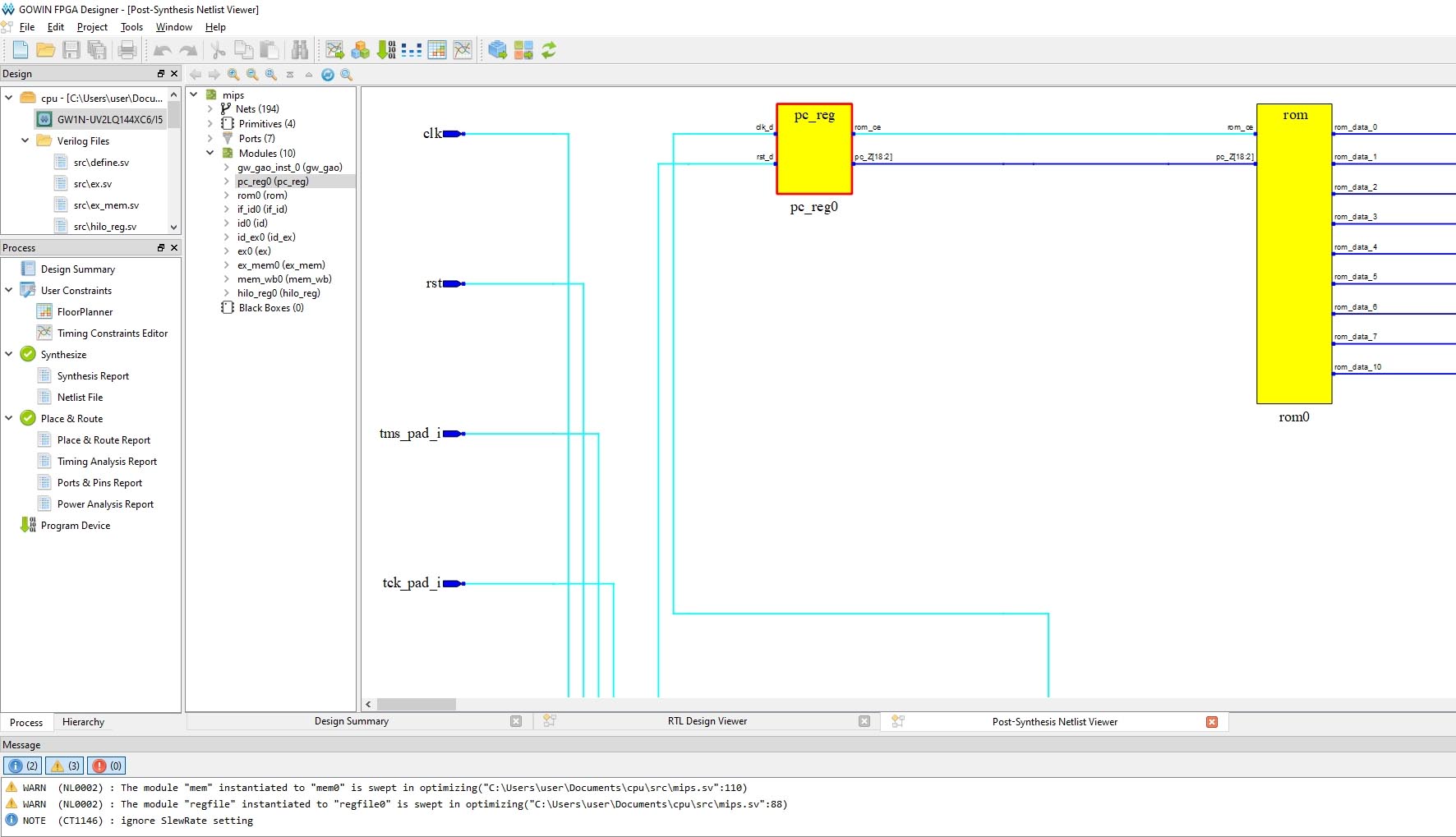

2. Synthesis & Implementation:

· Gowin Synthesis (GWINSYN): Proprietary synthesis engine optimized for Gowin FPGA architectures (LittleBee, Arora, etc.).

· Place-and-Route (PNR): Automated tools to map the synthesized logic onto the physical resources of the target FPGA.

· Timing Analysis: Static timing analysis (STA) to verify design meets clock frequency requirements.

3. Simulation & Verification:

· Integrated Waveform Viewer: For viewing simulation results.

· Support for Third-Party Simulators: Can generate simulation models for use with industry-standard simulators like ModelSim (requires separate license).

4. Programming & Debugging:

· Programmer (Gowin Programmer): Tools to generate the bitstream (.fs file) and program the FPGA via JTAG or other interfaces.

· In-System Logic Analyzer: Debugging tool to probe internal signals in the running FPGA (similar to ChipScope/SignalTap).

Key Advantages & Focus:

· Cost: Completely free with registration. No feature-limited “Web Edition.” This is a major advantage for startups, hobbyists, and educators.

· Vendor Optimization: Tightly integrated with Gowin’s FPGA families, often enabling better resource utilization for their chips than generic third-party tools.

· All-in-One Package: From HDL to programmed device in one software suite.

· Chinese & English Support: Full interface and documentation in both languages, reflecting Gowin’s market.

🖥️ System Requirements

Gowin EDA is a complex EDA suite with moderate to high hardware demands, similar to other FPGA tools. The minimum system requirements are a 64-bit operating system (Windows 10, or Linux distributions like CentOS 7/Ubuntu 18.04+), an Intel i5 or equivalent processor, 8 GB of RAM, 10 GB of free disk space, and a display with 1280×1024 resolution.

For recommended professional use to ensure smooth operation with medium to large designs, a system with Windows 10/11 Pro or a current Linux distribution, an Intel i7/Ryzen 7 processor or better, 16-32 GB of RAM, a solid-state drive (SSD) with 20+ GB free space, and a dedicated graphics card is strongly advised. A high-resolution monitor (1920×1080 or higher) significantly improves the IDE experience.

Price: 125 $

Price Currency: $

Operating System: Windows

Application Category: Electronics

Reviews

There are no reviews yet.